Global Fan-Out Wafer Level Packaging Market - Key Trends & Drivers Summarized

Why Is Fan-Out Wafer Level Packaging Emerging as the Future of Semiconductor Innovation?

Fan-out wafer level packaging (FOWLP) has rapidly ascended to the forefront of semiconductor packaging technologies due to its ability to deliver enhanced electrical performance, reduced form factor, and lower thermal resistance. This advanced packaging solution allows for a higher number of I/O connections without increasing chip size, making it ideally suited for applications that demand high functionality in compact devices. With traditional packaging technologies like wire bonding and flip chip reaching their performance limits, FOWLP provides a scalable and cost-efficient alternative that meets the growing demands of next-generation electronics. Its fan-out structure enables redistribution of the chip’ s I/Os over a larger area, eliminating the need for a substrate and reducing parasitic effects. The rising performance expectations in consumer electronics - especially in smartphones, wearables, AR/VR devices, and IoT nodes - are driving adoption, as FOWLP supports miniaturization while maintaining high-speed signal transmission. Additionally, the increased integration of artificial intelligence and 5G capabilities in compact form factors further necessitates advanced packaging techniques that can support heterogeneous integration, a key advantage of fan-out technology.How Are Advancements in Integration and Miniaturization Driving FOWLP Demand?

The surging need for multi-functional and miniaturized semiconductor devices is pushing the limits of conventional packaging and fueling demand for fan-out wafer level packaging. FOWLP supports both 2D and 3D integration, making it ideal for system-in-package (SiP) configurations where multiple chips or passives are packaged together. This becomes especially valuable in space-constrained devices like smartphones and wearables, where integrating functionalities like RF, power management, memory, and logic onto a single platform is increasingly critical. Recent advances in chiplet design, where larger functions are divided into smaller, reusable blocks, also align with FOWLP’ s strengths in interconnecting diverse dies with high interconnect density and low latency. Moreover, the rise of heterogeneous integration in data centers, automotive electronics, and high-performance computing (HPC) environments is accelerating the transition to FOWLP due to its superior thermal performance and electrical signal integrity. Fan-out solutions are also evolving with panel-level packaging (PLP), offering higher throughput and reduced cost per package, further broadening the technology’ s appeal. As chipmakers move toward energy-efficient, high-density architectures, FOWLP is emerging as a critical enabler for innovation in advanced electronics.Is the Semiconductor Ecosystem Adapting to Enable Large-Scale FOWLP Adoption?

A notable development in the fan-out wafer level packaging market is the increasing collaboration between semiconductor foundries, OSAT (outsourced semiconductor assembly and test) providers, and EDA tool developers to streamline FOWLP adoption. Major players such as TSMC, ASE, Amkor, and JCET are investing heavily in expanding their FOWLP production capacities and refining process capabilities to meet growing market demand. TSMC’ s InFO (Integrated Fan-Out) and ASE’ s FOCoS (Fan-Out Chip-on-Substrate) technologies are leading examples of proprietary FOWLP solutions tailored for specific applications in mobile and high-performance computing. Additionally, advancements in design automation tools are enabling faster layout optimization, signal integrity analysis, and thermal modeling for complex fan-out architectures. Equipment manufacturers are also developing specialized tools to handle larger panels, precise die placement, and ultra-fine RDL (redistribution layer) patterning - all essential for consistent FOWLP yields. Governments and industry alliances are further supporting the ecosystem with funding for R&D initiatives, particularly in Asia-Pacific and North America, where semiconductor self-sufficiency and technological leadership are strategic priorities. These developments indicate a maturing ecosystem that is increasingly capable of supporting high-volume, high-reliability FOWLP deployment across sectors.What Factors Are Driving the Rapid Growth of the Fan-Out Wafer Level Packaging Market?

The growth in the fan-out wafer level packaging market is driven by several factors related to packaging innovation, end-use expansion, and strategic manufacturing investments. On the technology front, the continued evolution of 5G, AI, and IoT devices is demanding higher performance and greater miniaturization, for which FOWLP offers a proven, scalable solution. The increasing adoption of chiplet-based architectures and heterogeneous integration across consumer electronics, automotive, and HPC applications is fueling demand for packaging technologies that allow dense interconnectivity with superior thermal and electrical efficiency. From an end-use perspective, the proliferation of ultra-thin smartphones, smartwatches, and edge AI devices is expanding FOWLP usage across multiple product categories. In the automotive industry, the push toward electrification and autonomous driving is creating strong demand for compact, reliable, and high-temperature-tolerant packaging solutions, where FOWLP has a distinct advantage. Additionally, increased investments by OSATs and foundries in advanced packaging lines - especially panel-level production - are improving economies of scale and lowering cost barriers for mass adoption. Regional policies encouraging semiconductor innovation and local manufacturing, particularly in Asia and the U.S., are further strengthening the supply chain and driving technological momentum. Collectively, these drivers are setting the stage for sustained and accelerated growth in the global FOWLP market.Report Scope

The report analyzes the Fan-Out Wafer Level Packaging market, presented in terms of market value. The analysis covers the key segments and geographic regions outlined below.- Segments: Process Type (Standard-Density Packaging, High-Density Packaging, Bumping); Business Model (OSAT, Foundry, IDM); Application (Consumer Electronics Application, Industrial Application, Automotive Application, Healthcare Application, Aerospace & Defense Application, IT & Telecommunications Application, Other Applications).

- Geographic Regions/Countries: World; United States; Canada; Japan; China; Europe (France; Germany; Italy; United Kingdom; Spain; Russia; and Rest of Europe); Asia-Pacific (Australia; India; South Korea; and Rest of Asia-Pacific); Latin America (Argentina; Brazil; Mexico; and Rest of Latin America); Middle East (Iran; Israel; Saudi Arabia; United Arab Emirates; and Rest of Middle East); and Africa.

Key Insights:

- Market Growth: Understand the significant growth trajectory of the Standard-Density Packaging segment, which is expected to reach US$2.8 Billion by 2030 with a CAGR of a 8.5%. The High-Density Packaging segment is also set to grow at 10.5% CAGR over the analysis period.

- Regional Analysis: Gain insights into the U.S. market, valued at $799.6 Million in 2024, and China, forecasted to grow at an impressive 14% CAGR to reach $1.1 Billion by 2030. Discover growth trends in other key regions, including Japan, Canada, Germany, and the Asia-Pacific.

Why You Should Buy This Report:

- Detailed Market Analysis: Access a thorough analysis of the Global Fan-Out Wafer Level Packaging Market, covering all major geographic regions and market segments.

- Competitive Insights: Get an overview of the competitive landscape, including the market presence of major players across different geographies.

- Future Trends and Drivers: Understand the key trends and drivers shaping the future of the Global Fan-Out Wafer Level Packaging Market.

- Actionable Insights: Benefit from actionable insights that can help you identify new revenue opportunities and make strategic business decisions.

Key Questions Answered:

- How is the Global Fan-Out Wafer Level Packaging Market expected to evolve by 2030?

- What are the main drivers and restraints affecting the market?

- Which market segments will grow the most over the forecast period?

- How will market shares for different regions and segments change by 2030?

- Who are the leading players in the market, and what are their prospects?

Report Features:

- Comprehensive Market Data: Independent analysis of annual sales and market forecasts in US$ Million from 2024 to 2030.

- In-Depth Regional Analysis: Detailed insights into key markets, including the U.S., China, Japan, Canada, Europe, Asia-Pacific, Latin America, Middle East, and Africa.

- Complimentary Updates: Receive free report updates for one year to keep you informed of the latest market developments.

Some of the 32 companies featured in this Fan-Out Wafer Level Packaging market report include:

- Amkor Technology Inc.

- Applied Materials Inc.

- ASE Technology Holding Co., Ltd.

- Deca Technologies Inc.

- Huatian Technology

- Infineon Technologies AG

- Intel Corporation

- JCET Group

- Lam Research Corporation

- Nepes Corporation

- NXP Semiconductors N.V.

- Powertech Technology Inc.

- Qualcomm Inc.

- Samsung Electronics Co. Ltd.

- Siliconware Precision Industries Co., Ltd. (SPIL)

- STMicroelectronics N.V.

- Taiwan Semiconductor Manufacturing Company Limited (TSMC)

- Texas Instruments Incorporated

- Unisem Group

- Veeco Instruments Inc.

This edition integrates the latest global trade and economic shifts into comprehensive market analysis. Key updates include:

- Tariff and Trade Impact: Insights into global tariff negotiations across 180+ countries, with analysis of supply chain turbulence, sourcing disruptions, and geographic realignment. Special focus on 2025 as a pivotal year for trade tensions, including updated perspectives on the Trump-era tariffs.

- Adjusted Forecasts and Analytics: Revised global and regional market forecasts through 2030, incorporating tariff effects, economic uncertainty, and structural changes in globalization. Includes historical analysis from 2015 to 2023.

- Strategic Market Dynamics: Evaluation of revised market prospects, regional outlooks, and key economic indicators such as population and urbanization trends.

- Innovation & Technology Trends: Latest developments in product and process innovation, emerging technologies, and key industry drivers shaping the competitive landscape.

- Competitive Intelligence: Updated global market share estimates for 2025, competitive positioning of major players (Strong/Active/Niche/Trivial), and refined focus on leading global brands and core players.

- Expert Insight & Commentary: Strategic analysis from economists, trade experts, and domain specialists to contextualize market shifts and identify emerging opportunities.

Table of Contents

Companies Mentioned (Partial List)

A selection of companies mentioned in this report includes, but is not limited to:

- Amkor Technology Inc.

- Applied Materials Inc.

- ASE Technology Holding Co., Ltd.

- Deca Technologies Inc.

- Huatian Technology

- Infineon Technologies AG

- Intel Corporation

- JCET Group

- Lam Research Corporation

- Nepes Corporation

- NXP Semiconductors N.V.

- Powertech Technology Inc.

- Qualcomm Inc.

- Samsung Electronics Co. Ltd.

- Siliconware Precision Industries Co., Ltd. (SPIL)

- STMicroelectronics N.V.

- Taiwan Semiconductor Manufacturing Company Limited (TSMC)

- Texas Instruments Incorporated

- Unisem Group

- Veeco Instruments Inc.

Table Information

| Report Attribute | Details |

|---|---|

| No. of Pages | 377 |

| Published | May 2026 |

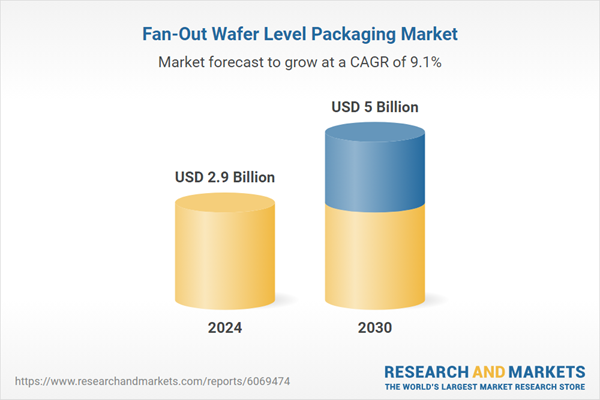

| Forecast Period | 2024 - 2030 |

| Estimated Market Value ( USD | $ 2.9 Billion |

| Forecasted Market Value ( USD | $ 5 Billion |

| Compound Annual Growth Rate | 9.1% |

| Regions Covered | Global |