Global Gate-All-Around FET (GAAFET) Market - Key Trends & Drivers Summarized

Why Is Gate-All-Around FET Architecture Reshaping Advanced Semiconductor Nodes?

Gate-All-Around Field Effect Transistors (GAAFETs) are emerging as the next major advancement in transistor architecture for nanoscale semiconductor processes. Unlike FinFETs, which control current from three sides of the channel, GAAFETs surround the channel with gate material on all sides, providing enhanced electrostatic control. This configuration improves performance, reduces leakage, and supports further device scaling below 3 nanometers.As traditional planar and FinFET structures approach physical and electrical limits, GAAFETs offer improved short-channel behavior and better threshold voltage control. Foundries are transitioning to GAAFETs to continue Moore’s Law scaling and deliver high-performance, low-power chips for mobile processors, AI accelerators, and high-speed networking. The architecture allows more compact layouts while supporting variations in gate width, offering enhanced design flexibility for power-performance optimization.

How Are Fabrication Processes and Materials Evolving to Enable GAAFET Adoption?

GAAFET implementation requires significant changes in materials and process flow. Key fabrication steps include epitaxial growth of stacked nanosheets or nanowires, precision etching, and conformal gate deposition. Gate length uniformity, nanosheet spacing, and inner spacer formation are critical for maintaining electrical characteristics and yield. High-k metal gate stacks, advanced lithography, and atomic layer deposition are used to maintain dimensional accuracy.Device manufacturers are also leveraging strain engineering and dielectric engineering to enhance carrier mobility and reduce variability. Multi-Vt GAAFET libraries are being developed to offer broader design coverage across power envelopes. EDA toolchains are adapting to GAAFET topologies, with updated modeling and verification flows to support parasitic extraction and electrothermal simulation. These process and design adaptations are necessary for smooth integration into 2 nm and sub-2 nm logic nodes.

Where Are GAAFETs Expected to Be Deployed First and Which End-Uses Are Targeted?

Initial GAAFET adoption is focused on mobile SoCs, data center CPUs, and AI chips where power efficiency and density are critical. Leading semiconductor foundries and IDMs are planning commercial deployment of GAAFET-based nodes starting with 2 nm-class production. High-performance computing applications benefit from GAAFET’s low leakage and reduced variability, especially in multi-core architectures and advanced packaging environments.Beyond logic chips, there is ongoing research into GAAFET application in memory, RF, and sensor integration. Their superior electrostatics support tighter device packing, enabling improved energy efficiency in edge computing, AR/VR processors, and autonomous systems. Adoption will accelerate as design flows, IP ecosystems, and foundry support mature. Integration into heterogeneous 3D ICs and chiplets is expected to follow as thermal and interconnect challenges are addressed.

What Is Driving Growth in the Gate-All-Around FET Market?

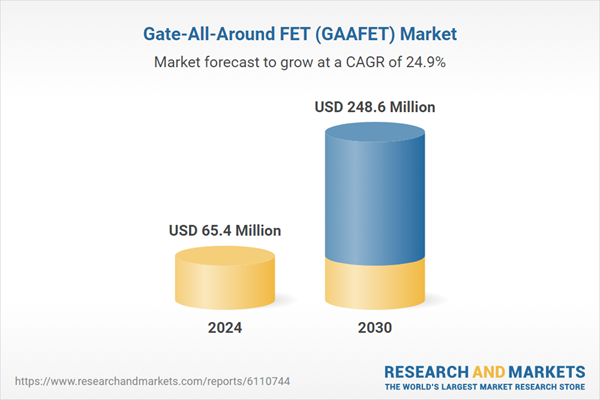

Growth in the GAAFET market is driven by several factors related to transistor scaling, power efficiency requirements, and advanced node readiness. Demand for sub-3 nm semiconductors in mobile, AI, and high-performance computing is pushing adoption of gate-all-around architecture. Advances in nanosheet fabrication, spacer engineering, and gate material deposition are enabling commercial viability. Growth is also supported by foundry transitions to GAAFET platforms, increasing need for performance-density tradeoffs, and continued development of design enablement tools and process integration strategies. As FinFET limitations intensify, GAAFET becomes essential for sustaining performance and energy scaling in next-generation semiconductor devices.Scope of the Report

The report analyzes the Gate-All-Around FET (GAAFET) market, presented in terms of market value (USD). The analysis covers the key segments and geographic regions outlined below:- Segments: Size (2nm Size, 3nm Size); Application (Inverters & UPS Application, Consumer Electronics Application, Industrial Systems Application).

- Geographic Regions/Countries: World; United States; Canada; Japan; China; Europe (France; Germany; Italy; United Kingdom; Spain; Russia; and Rest of Europe); Asia-Pacific (Australia; India; South Korea; and Rest of Asia-Pacific); Latin America (Argentina; Brazil; Mexico; and Rest of Latin America); Middle East (Iran; Israel; Saudi Arabia; United Arab Emirates; and Rest of Middle East); and Africa.

Key Insights:

- Market Growth: Understand the significant growth trajectory of the 2nm Size segment, which is expected to reach US$133.1 Million by 2030 with a CAGR of a 22.1%. The 3nm Size segment is also set to grow at 28.8% CAGR over the analysis period.

- Regional Analysis: Gain insights into the U.S. market, valued at $17.8 Million in 2024, and China, forecasted to grow at an impressive 32.5% CAGR to reach $59.6 Million by 2030. Discover growth trends in other key regions, including Japan, Canada, Germany, and the Asia-Pacific.

Why You Should Buy This Report:

- Detailed Market Analysis: Access a thorough analysis of the Global Gate-All-Around FET (GAAFET) Market, covering all major geographic regions and market segments.

- Competitive Insights: Get an overview of the competitive landscape, including the market presence of major players across different geographies.

- Future Trends and Drivers: Understand the key trends and drivers shaping the future of the Global Gate-All-Around FET (GAAFET) Market.

- Actionable Insights: Benefit from actionable insights that can help you identify new revenue opportunities and make strategic business decisions.

Key Questions Answered:

- How is the Global Gate-All-Around FET (GAAFET) Market expected to evolve by 2030?

- What are the main drivers and restraints affecting the market?

- Which market segments will grow the most over the forecast period?

- How will market shares for different regions and segments change by 2030?

- Who are the leading players in the market, and what are their prospects?

Report Features:

- Comprehensive Market Data: Independent analysis of annual sales and market forecasts in US$ Million from 2024 to 2030.

- In-Depth Regional Analysis: Detailed insights into key markets, including the U.S., China, Japan, Canada, Europe, Asia-Pacific, Latin America, Middle East, and Africa.

- Company Profiles: Coverage of players such as Applied Materials, ASML Holding, Cadence Design Systems, GlobalFoundries, IBM and more.

- Complimentary Updates: Receive free report updates for one year to keep you informed of the latest market developments.

Some of the 39 companies featured in this Gate-All-Around FET (GAAFET) market report include:

- Applied Materials

- ASML Holding

- Cadence Design Systems

- GlobalFoundries

- IBM

- Imec

- Infineon Technologies

- Intel Corporation

- Lam Research Corporation

- MediaTek Inc.

- Micron Technology

- NXP Semiconductors

- Qualcomm Incorporated

- Samsung Electronics

- Semiconductor Manufacturing International Corporation (SMIC)

- Synopsis, Inc.

- Taiwan Semiconductor Manufacturing Company (TSMC)

- Texas Instruments

- Tokyo Electron Limited

- Western Digital

This edition integrates the latest global trade and economic shifts into comprehensive market analysis. Key updates include:

- Tariff and Trade Impact: Insights into global tariff negotiations across 180+ countries, with analysis of supply chain turbulence, sourcing disruptions, and geographic realignment. Special focus on 2025 as a pivotal year for trade tensions, including updated perspectives on the Trump-era tariffs.

- Adjusted Forecasts and Analytics: Revised global and regional market forecasts through 2030, incorporating tariff effects, economic uncertainty, and structural changes in globalization. Includes historical analysis from 2015 to 2023.

- Strategic Market Dynamics: Evaluation of revised market prospects, regional outlooks, and key economic indicators such as population and urbanization trends.

- Innovation & Technology Trends: Latest developments in product and process innovation, emerging technologies, and key industry drivers shaping the competitive landscape.

- Competitive Intelligence: Updated global market share estimates for 2025 (E), competitive positioning of major players (Strong/Active/Niche/Trivial), and refined focus on leading global brands and core players.

- Expert Insight & Commentary: Strategic analysis from economists, trade experts, and domain specialists to contextualize market shifts and identify emerging opportunities.

Table of Contents

Companies Mentioned (Partial List)

A selection of companies mentioned in this report includes, but is not limited to:

- Applied Materials

- ASML Holding

- Cadence Design Systems

- GlobalFoundries

- IBM

- Imec

- Infineon Technologies

- Intel Corporation

- Lam Research Corporation

- MediaTek Inc.

- Micron Technology

- NXP Semiconductors

- Qualcomm Incorporated

- Samsung Electronics

- Semiconductor Manufacturing International Corporation (SMIC)

- Synopsis, Inc.

- Taiwan Semiconductor Manufacturing Company (TSMC)

- Texas Instruments

- Tokyo Electron Limited

- Western Digital

Table Information

| Report Attribute | Details |

|---|---|

| No. of Pages | 273 |

| Published | May 2026 |

| Forecast Period | 2024 - 2030 |

| Estimated Market Value ( USD | $ 65.4 Million |

| Forecasted Market Value ( USD | $ 248.6 Million |

| Compound Annual Growth Rate | 24.9% |

| Regions Covered | Global |