Speak directly to the analyst to clarify any post sales queries you may have.

Comprehensive framing of gallium arsenide wafer fabrication fundamentals linking materials science, process choice, and device-level performance imperatives

Gallium arsenide wafer fabrication occupies a pivotal niche where material science, precision manufacturing, and high-frequency device requirements intersect. This executive summary synthesizes technological pathways, supply chain pressures, and end-user demand signals that are currently shaping decision-making across fabrication plants, device manufacturers, and systems integrators. The fabric of the industry is defined by process control, epitaxial quality, and wafer size logistics, which together determine yield, device performance, and downstream integration complexity.Throughout the introduction, it is important to frame GaAs not as a commodity substrate but as an enabler of specialized capabilities in optoelectronics, radio frequency systems, and certain photovoltaic applications. Manufacturing methods such as metal organic chemical vapor deposition and molecular beam epitaxy drive material properties at the atomic scale, while liquid phase epitaxy remains relevant in select legacy and high-throughput contexts. In parallel, polarity, wafer size, and end-user requirements create a mosaic of production practices that vary by application and region. Understanding these intersecting factors establishes the foundation for the subsequent sections, which examine transformative landscape shifts, policy impacts, segmentation intelligence, and recommended actions for industry leaders.

Detailed examination of converging technological advances and supply chain restructuring that are redefining capacity, capability, and commercial dynamics

The landscape of GaAs wafer fabrication is undergoing transformative shifts driven by technology innovation, supply chain reconfiguration, and evolving end-market requirements. On the technology front, improvements in epitaxial growth techniques and automation have narrowed variability in material quality, enabling higher yield and tighter device performance tolerances, which in turn expand design possibilities for RF and optoelectronic applications. Meanwhile, advances in inspection, metrology, and in-line process control are migrating learnings from other semiconductor segments into III-V manufacturing, yielding step changes in reproducibility and throughput.Concurrently, supply chains are being rebalanced as companies pursue resilience and geographic diversification. This trend is accelerating investments in regional capacity, strategic partnerships with substrate and tooling suppliers, and the reassessment of single-source dependencies. End-user dynamics are also shifting: the telecommunications and aerospace sectors are demanding wafers with tailored electrical and optical characteristics, while automotive and consumer electronics are pressing manufacturers to reconcile cost, reliability, and volume constraints. The combined effect is an industry that is simultaneously becoming more specialized in capability and more distributed in production footprint, creating new strategic imperatives for players across the value chain.

Analytical perspective on how tariff-driven policy shifts are reshaping sourcing strategies, contractual risk profiles, and regional production decisions in fabrication

Recent tariff measures introduced by the United States have produced layered effects across procurement, sourcing strategies, and supplier relations within the GaAs wafer ecosystem. At the procurement level, tariffs have increased the emphasis on total landed cost rather than unit price alone, prompting buyers to reassess supplier contracts and evaluate alternative sourcing corridors. As a result, there is heightened scrutiny on origin transparency, customs classification, and compliance processes to avoid unexpected duty exposure.For manufacturers and contract fabricators, tariffs have influenced decisions on where to locate value-added activities such as epitaxial growth, dicing, and packaging. Some firms are accelerating regionalization strategies to mitigate tariff exposure and to maintain near-term commercial continuity, while others are pursuing long-term contractual protections or tariff-mitigation techniques. The cumulative effect is a reallocation of transactional and operational risk: firms with deep supplier relationships and flexible production footprints have a comparative advantage in adapting quickly, whereas those with concentrated upstream dependencies face greater disruption risk. In sum, the tariff environment has catalyzed a strategic reassessment of sourcing and production models across the GaAs wafer supply chain.

In-depth segmentation synthesis connecting wafer formats, application subdomains, industrial end-users, epitaxial techniques, and substrate polarity to operational choices

Segmentation insights reveal how wafer size, application domains, end-user industries, technology choices, and polarity intersect to determine manufacturing priorities and product roadmaps. Wafer size matters because production economics, equipment compatibility, and handling protocols differ materially between four inch, six inch, and eight inch diameters; manufacturers must align capacity planning and tooling investments with the wafer formats most prevalent in their target applications. Application segmentation spans optoelectronics, photovoltaic deployments, and RF applications, where optoelectronics itself branches into laser diodes, light emitting diodes, and photodetectors; photovoltaic use cases separate into space-qualified and terrestrial installations; and RF deployments encompass mobile communication, radar and defense, and satellite communication, each presenting unique performance and qualification demands.End-user industry dynamics further influence fabrication choices: aerospace and defense impose stringent qualification and traceability requirements, while automotive prioritizes functional safety and long-term supply commitments, and consumer electronics emphasizes cost and integration density. Technology selection-whether liquid phase epitaxy, metal organic chemical vapor deposition, or molecular beam epitaxy-governs achievable material properties, layer uniformity, and throughput trade-offs. Finally, wafer polarity, across N type, P type, and semi-insulating substrates, directly affects device behavior and process flows. Taken together, these segmentation vectors create a complex decision matrix that manufacturers must navigate to optimize product fit and operational efficiency.

Comparative regional overview of how geographic ecosystems influence capacity choices, qualification norms, and collaborative pathways in fabrication and supply chains

Regional dynamics exert powerful influence over capacity planning, logistics, and collaborative partnerships in GaAs wafer fabrication. In the Americas, activity centers emphasize defense, aerospace, and advanced communications applications, supported by a network of specialized foundries and system integrators that prioritize qualification standards and secure supply chains. This region’s ecosystem often favors close collaboration between material suppliers and system manufacturers to accelerate iterations and to meet defense-related procurement rigor.Europe, Middle East & Africa exhibit a mix of high-reliability industrial programs and emergent commercial deployments. In this geography, regulatory regimes and industrial policy considerations shape investment decisions, while partnerships between research institutions and fabricators help drive niche capabilities in photonics and high-frequency systems. Meanwhile, Asia-Pacific represents a dense concentration of manufacturing capacity, vertically integrated supply chains, and rapid adoption in telecommunications and consumer-facing markets. This region’s scale and supplier variety make it a focal point for both tooling innovation and incremental process refinement. Across these geographies, differences in labor cost, regulatory expectations, and supplier ecosystems determine not only where wafers are produced but how production is organized and governed.

Strategic corporate positioning and partnership patterns that determine competitive advantage in process excellence, integration, and specialized service offerings

Competitive dynamics among companies in the GaAs wafer ecosystem reflect a balance between captive manufacturing strategies and specialized service models. Some firms focus on integrated supply, offering end-to-end capabilities from substrate sourcing through epitaxial growth and dicing, which provides customers with simplified procurement and tighter quality control. Other players specialize in niche process steps-such as advanced epitaxy or defect reduction techniques-allowing them to command premium positioning based on technical differentiation.Strategic partnerships and joint development initiatives are increasingly common as companies seek to lower technical risk and accelerate time-to-market. Original equipment manufacturers prize suppliers that can demonstrate consistent material uniformity, traceable process parameters, and documented qualification pathways. Meanwhile, contract manufacturers that invest in flexible toolsets and modular cleanroom capacity can adapt more quickly to shifting wafer formats and application requirements. Intellectual property around epitaxial recipes, metrology methods, and yield improvement approaches becomes a critical asset, driving both collaboration agreements and selective vertical integration within the value chain.

Action-oriented strategic initiatives for leaders to strengthen resilience, accelerate qualification, and convert process excellence into market advantage

Industry leaders should pursue a set of actionable initiatives that reinforce supply resilience, elevate technical differentiation, and align production footprints with strategic customer needs. First, prioritize investments in epitaxial process control and in-line metrology to reduce variability and accelerate qualification timelines; this technical focus yields downstream benefits in yield and device performance that are critical for high-reliability segments. Second, diversify supplier and production pathways to reduce single-source dependency, combining regional capacity with strategic long-term agreements to manage geopolitical and tariff-related risk.Third, deepen collaboration with key end-users in aerospace, automotive, telecom, and consumer electronics to co-develop wafer specifications that balance performance with manufacturability. Fourth, formalize intellectual property and data governance practices to protect process know-how while enabling controlled collaboration with research partners. Finally, align commercial contracting to reflect total landed cost and supply continuity rather than unit price alone. By executing these priorities, leaders can transform macro-level pressures into competitive advantages, improving responsiveness to customer needs while safeguarding operational continuity.

Transparent mixed-method research approach combining expert interviews, technical literature synthesis, and supply chain mapping to derive pragmatic industry insights

The research behind this summary employs a multi-disciplinary approach that integrates primary interviews, technical literature review, and supply chain analysis to ensure robust and balanced findings. Qualitative insights derive from conversations with manufacturing leaders, process engineers, and procurement specialists across wafer fabrication, epitaxy tooling, and device integration segments. These discussions were complemented by a targeted review of peer-reviewed technical papers, standards documentation, and trade publications to validate process characteristics and technology trajectories.Supply chain framing relied on mapping supplier relationships, equipment dependencies, and logistics pathways, with attention to regional trade flows and policy impacts. The methodology emphasizes triangulation: cross-validating interview insights with documented process capabilities and publicly available operational practices to mitigate single-source bias. Throughout the research process, care was taken to maintain confidentiality for proprietary sources while extracting actionable patterns and strategic implications. This methodological combination yields a pragmatic understanding of both technical and commercial facets of GaAs wafer fabrication.

Concluding synthesis highlighting the interplay of technological refinement, supply resilience, and customer alignment that will determine competitive outcomes in fabrication

In conclusion, the GaAs wafer fabrication landscape is defined by nuanced trade-offs between process capability, supply chain resilience, and application-driven performance requirements. Technological improvements in epitaxial growth and metrology are enabling greater material consistency, while geopolitical and trade considerations are prompting strategic relocation and diversification of production footprints. These forces operate together to create both challenges and opportunities for manufacturers, suppliers, and system integrators.Going forward, success will favor organizations that invest in process precision, cultivate flexible supplier networks, and engage deeply with end-users to co-develop specifications that balance performance and manufacturability. Firms that align technical investment with strategic sourcing and robust contracting will be better positioned to capture demand in high-reliability and high-performance segments. By synthesizing the technical, commercial, and policy dimensions covered in this summary, decision-makers can prioritize actions that reinforce resilience and unlock sustainable competitive advantage in GaAs wafer fabrication.

Table of Contents

7. Cumulative Impact of Artificial Intelligence 2025

17. China GaAs Wafer Fabrication Market

Companies Mentioned

- Ampleon Netherlands B.V.

- Analog Devices Inc.

- Broadcom Inc.

- Fujitsu Limited

- Infineon Technologies AG

- Laird Connectivity Inc.

- MACOM Technology Solutions Holdings Inc.

- Maxim Integrated Products Inc.

- Microchip Technology Inc.

- Mitsubishi Electric Corporation

- NEC Corporation

- NXP Semiconductors N.V.

- ON Semiconductor Corporation

- Panasonic Corporation

- Qorvo Inc.

- Skyworks Solutions Inc.

- STMicroelectronics N.V.

- Texas Instruments Incorporated

- Toshiba Electronic Devices & Storage Corporation

- Wolfspeed Inc.

Table Information

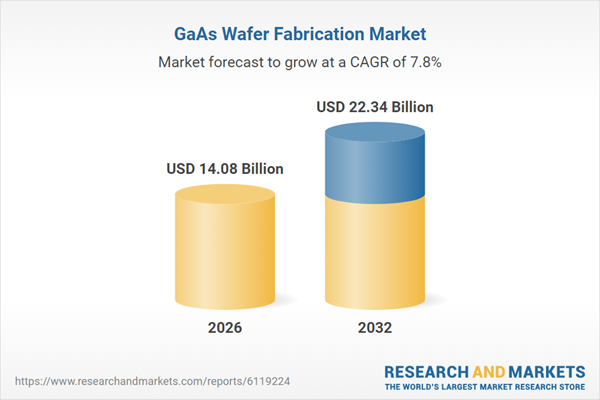

| Report Attribute | Details |

|---|---|

| No. of Pages | 195 |

| Published | January 2026 |

| Forecast Period | 2026 - 2032 |

| Estimated Market Value ( USD | $ 14.08 Billion |

| Forecasted Market Value ( USD | $ 22.34 Billion |

| Compound Annual Growth Rate | 7.7% |

| Regions Covered | Global |

| No. of Companies Mentioned | 20 |