Speak directly to the analyst to clarify any post sales queries you may have.

The CPU Instruction Set Architecture (ISA) market stands at the core of enterprise-grade compute strategies, shaping how businesses approach software portability, security, and infrastructure agility across an evolving digital landscape. Organizations evaluating platform roadmaps rely on understanding this market to align technology investments with long-term operational resilience.

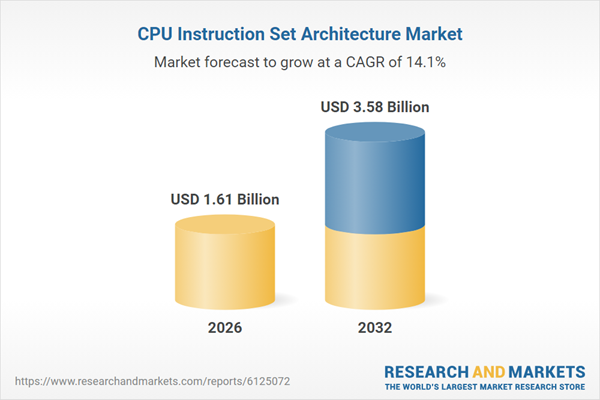

Market Snapshot: CPU Instruction Set Architecture Market Size and Growth

The CPU Instruction Set Architecture market is projected to expand from USD 1.42 billion in 2025 to USD 1.61 billion in 2026, reaching USD 3.58 billion by 2032 at a CAGR of 14.08%. Growth is driven by adoption of heterogeneous computing models, demand for multi-architecture compatibility, and heightened emphasis on robust security across both software and hardware platforms. Enterprises are increasingly investing in ISAs that support diverse workloads, reduce integration friction, and strengthen operational continuity in an environment of global supply-chain variability.

Scope & Segmentation

- Platform Types: Desktop, laptop, server, cloud data center, embedded, mobile, automotive, industrial, and telecom workloads define where ISAs are deployed to maximize compute efficiency.

- ISA Types: x86, ARM, RISC-V, and custom or specialized architectures, each tailored for deterministic performance, legacy compatibility, or niche certification requirements.

- Application Domains: Consumer electronics, automotive control, industrial automation, telecom infrastructure, networking, artificial intelligence, and machine learning rely on ISA choices to optimize diverse implementations.

- End User Segments: Enterprises, cloud service providers, OEMs, ODMs, governments, defense organizations, and SMEs leverage ISA advancements to align with security, compliance, and scalability priorities and operational needs.

- Channel Strategies: OEM and ODM-led distribution, direct enterprise sales, online channels, and developer or distributor networks determine how new ISA solutions reach critical market segments.

- Geographies: Adoption trends and ecosystem maturity vary across the Americas, Europe, Middle East, Africa, and Asia-Pacific, reflecting regional compliance, resource availability, and strategic priorities.

- Technology Enablers: Vector operations, hardware cryptography, memory safety features, virtualization layers, secure enclave support, standardized toolchains, continuous integration capabilities, and modular IP all play pivotal roles in defining the competitive landscape.

- Key Decision Factors: Backward compatibility, integrated security measures, energy efficiency, resilient supply-chain integration, mature ecosystem support, and alignment with regional compliance standards drive ISA selection criteria.

Key Takeaways: ISA as a Strategic Lever

- ISA selection shapes technology direction for years, affecting portability and the ability to adapt workloads across new and legacy environments.

- As heterogeneous compute becomes widespread, CPUs increasingly coordinate task execution between accelerators and specialized devices; ISA features for dispatch and data movement are critical.

- Open ISA adoption is enabling more organizations to add custom extensions and create region-specific supply chains, while proprietary ISAs retain appeal due to deep toolchain support and certified integrations.

- Security is a baseline expectation as organizations move toward confidential computing, secure enclaves, and memory safety as standard ISA features in enterprise platforms.

- Ecosystem completeness—including robust compiler, library, and profiler support—determines how rapidly companies can deploy new architectures, often outweighing raw performance alone.

- With tools such as containerization and architecture-aware compilation, organizations are fast-tracking software portability and preparing for seamless transitions between ISAs as workloads evolve.

Tariff Impact and Supply-Chain Diversification

- Tariffs in key markets, particularly the United States, are amplifying supply pressures and causing a shift toward procurement diversification and regionalized assembly.

- Organizations are actively qualifying additional suppliers and adapting bill-of-materials strategies, which contributes to changes in ISA ecosystem adoption, especially in cost-driven sectors and applications requiring long product lifecycles.

- Software development teams emphasize portability and abstraction, with increased investments in cross-architecture toolchains and verified translation, reducing dependency on any single vendor environment.

- Resilience planning now includes maintaining support for alternative ISAs—using emulation or intermediate representations in compilers—to enable rapid adjustments in response to shifts in hardware supply or regulatory landscape.

Methodology & Data Sources

This report synthesizes insights from primary interviews with silicon, platform, and software engineering stakeholders, complemented by a detailed mapping of certified ISAs, toolchain capabilities, and regional adoption. The analysis incorporates secondary data from standards reviews, open-source activity, vendor documentation, and regulatory sources, with a triangulation approach to ensure reliable and actionable conclusions.

Why This Report Matters: CPU Instruction Set Architecture Market

- Supports executive and technical leadership in minimizing migration and supply risk while streamlining platform investment decisions.

- Clarifies dynamics and practical steps for multi-architecture readiness and secure execution tailored to unique organizational contexts.

- Illuminates how regional market forces and ecosystem strategies shape resilient and future-aligned ISA selection for sustained competitiveness.

Conclusion

Strategic ISA choices underpin platform resilience and adaptability. Senior leaders who prioritize ecosystem robustness and integrated security approaches can better align with evolving operational demands and regional compliance requirements.

Table of Contents

7. Cumulative Impact of Artificial Intelligence 2025

16. China CPU Instruction Set Architecture Market

Companies Mentioned

The key companies profiled in this CPU Instruction Set Architecture market report include:- Advanced Micro Devices Inc.

- Ampere Computing LLC

- Apple Inc.

- Arm Limited

- Broadcom Inc.

- Cadence Design Systems Inc.

- Esperanto Technologies Inc.

- Fujitsu Limited

- Google LLC

- Infineon Technologies AG

- Intel Corporation

- International Business Machines Corporation

- Loongson Technology Corporation Limited

- Marvell Technology Group Ltd.

- MediaTek Inc.

- Microsoft Corporation

- NVIDIA Corporation

- NXP Semiconductors N.V.

- Oracle Corporation

- Qualcomm Incorporated

- Renesas Electronics Corporation

- Samsung Electronics Co., Ltd.

- SiFive Inc.

- Texas Instruments Incorporated

- VIA Technologies Inc.

- Zhaoxin Semiconductor Co., Ltd.

Table Information

| Report Attribute | Details |

|---|---|

| No. of Pages | 193 |

| Published | January 2026 |

| Forecast Period | 2026 - 2032 |

| Estimated Market Value ( USD | $ 1.61 Billion |

| Forecasted Market Value ( USD | $ 3.58 Billion |

| Compound Annual Growth Rate | 14.0% |

| Regions Covered | Global |

| No. of Companies Mentioned | 27 |