Speak directly to the analyst to clarify any post sales queries you may have.

An authoritative introduction to SerDes evolution, design tradeoffs, and systems-level considerations that drive architecture and procurement decisions

The SerDes (Serializer/Deserializer) landscape stands at the intersection of high-speed data transmission engineering and system-level architectural evolution. Modern design requirements extend beyond raw throughput to encompass power efficiency, signal integrity, physical integration, and protocol interoperability. As compute and connectivity demands have grown, system architects have increasingly looked for SerDes solutions that balance advanced process technologies with resilient analog front ends and scalable IP cores. Consequently, suppliers are navigating complex tradeoffs between leading-edge nodes that offer performance advantages and mature nodes that deliver robustness and cost efficiency.Transitioning from component-level optimization to platform-level integration, engineering teams are prioritizing tighter alignment between SerDes performance envelopes and end-market application profiles. This shift requires closer collaboration between silicon designers, module vendors, and hyperscale system integrators in order to match lane counts, reach characteristics, and interface standards to real-world workloads. Moreover, quality and reliability considerations such as thermal behavior, electromagnetic compatibility, and long-term supply continuity are now intrinsic to procurement discussions.

Given these dynamics, decision-makers must evaluate SerDes solutions through lenses of interoperability, manufacturability, and long-term maintainability. Strategic procurement and product planning hinge on selecting partners and architectures that support evolving interface standards, diverse transmission media, and heterogeneous packaging approaches while enabling predictable roadmaps for future upgrades.

How converging advances in compute, packaging, and protocol development are reshaping SerDes architectures and vendor strategies across the value chain

The SerDes ecosystem is experiencing transformative shifts driven by several converging technological and market forces. Data-centric computing architectures, the proliferation of AI accelerators, and the expanding role of high-bandwidth interconnects have elevated the importance of lane-level performance and interface versatility. At the same time, packaging innovations such as co-packaged optics and multi-chip modules are redefining where SerDes functionality resides within a system, with implications for thermal management, board-level routing, and optical-electrical partitioning.Concurrently, protocol evolution is accelerating: Ethernet and PCIe variants are advancing in tandem, and designers must account for both established standards and emergent interface requirements. This multi-protocol reality is prompting a shift toward configurable transceivers and soft IP that can be retargeted across product families. Power-profile stratification has also become a decisive differentiator; markets that demand low-power solutions for edge devices contrast sharply with data center environments where high-performance profiles are prioritized.

These shifts imply a reorientation of vendor strategies toward modular IP portfolios, flexible supply agreements, and expedited co-development cycles with hyperscalers and OEMs. In turn, procurement organizations must re-evaluate supplier selection criteria to factor in roadmap alignment, integration support, and the ability to co-engineer solutions that bridge silicon, packaging, and optical subsystems. As a result, competition is increasingly shaped by systems-level capabilities rather than isolated transistor-level performance.

The cumulative effects of recent tariff-driven policy shifts on SerDes supply chains, procurement strategies, and operational resilience across global operations

The policy environment in 2025 introduced additional complexity to global supply chains and sourcing strategies for semiconductor components, including SerDes chips. Tariff measures and regulatory changes have influenced cost structures, supplier selection, and geographic diversification strategies. While tariffs alone are not the only determinant of sourcing decisions, they act as a catalyst that compels original equipment manufacturers and component suppliers to reassess production footprints and to revisit nearshoring or multi-sourcing approaches.Consequently, companies have placed greater emphasis on supply resilience and regulatory compliance. Procurement teams increasingly integrate tariff scenarios into procurement contracts and evaluate total landed costs rather than relying solely on unit price comparisons. This holistic cost view accounts for logistics, inventory buffering, and potential requalification expenses when moving production between foundries or assembly sites. Moreover, compliance and traceability mechanisms have been strengthened to ensure that components meet changing policy requirements without disrupting product certifications or time-to-market.

In response to these cumulative policy effects, some vendors have accelerated partnerships with foundries and assembly houses in diversified geographies and adapted product roadmaps to favor platforms that are less sensitive to cross-border supply constraints. As a result, corporate strategy now blends commercial, operational, and policy considerations to maintain competitive positioning while minimizing exposure to sudden changes in trade policy.

A granular analysis of segmentation axes that delineate technical priorities and commercial pathways across data rate, interface, packaging, and application vectors in SerDes design

Segment-level dynamics illuminate how SerDes requirements diverge across technical and commercial use cases, guiding where innovation and investment yield the greatest returns. Based on Data Rate Per Lane (Gbps), designers must account for a spectrum that includes categories from sub-gigabit connectivity to ultra-high-rate lanes above 400 Gbps; each range imposes distinct analog front-end design challenges, equalization strategies, and channel modeling priorities. In parallel, end markets shape product feature sets: aerospace and defense prioritize ruggedization and long-term lifecycle support, automotive emphasizes functional safety and electromagnetic resilience for advanced driver assistance and in-vehicle networking, while data center applications require optimization for AI accelerators, network interface cards, optical modules, and high-port-count switches.Interface standard protocols further delineate product expectations. Ethernet variants across multiple data rates and PCIe generations demand flexible PHY designs and robust compliance testing regimes. Fibre Channel, SAS, SATA, HDMI/DisplayPort, and USB each bring their own signal integrity and protocol-handling requirements. Transmission medium decisions-whether optical fiber, electrical copper, backplane, or co-packaged optics-affect reach characteristics and integration complexity; optical fiber variants such as integrated photonics versus pluggable modules present divergent tradeoffs between performance and serviceability.

Product-type segmentation distinguishes discrete ASIC SerDes, integrated SoC SerDes, standalone transceivers, serializer-only or deserializer-only components, PHY analog front ends, and IP cores that are offered as hard or soft IP. Lane counts ranging from single and dual lanes to quad, octal, and 16-plus configurations drive layout and power-distribution considerations. Reach classifications from short and medium reach to long reach and ultra-long reach coherent solutions influence module design and testing strategies. Packaging and integration options-including co-packaged optics, multi-chip modules, pluggable compatibility, SoC integration, and standalone chips-determine thermal profiles and assembly workflows. Technology node choices between advanced nodes (16 to 28nm), leading-edge nodes (7nm and below), and mature nodes above 28nm affect tradeoffs among power, cost, and yield. Finally, power profiles spanning low-power, balanced, and high-performance categories inform target applications and support ecosystems. Taken together, these segmentation axes create a multidimensional design and commercialization matrix in which product architectures must be optimized along mutually constraining technical and commercial vectors.

How diverse regional demand drivers, manufacturing footprints, and policy frameworks shape SerDes supply chain strategies across the Americas, EMEA, and Asia-Pacific

Regional dynamics continue to define competitive positioning and supply chain design for SerDes technologies, with each geography exhibiting differentiated end-market demand, manufacturing capabilities, and policy landscapes. In the Americas, demand patterns are heavily influenced by hyperscale data center operations, a vibrant ecosystem of networking equipment suppliers, and targeted government initiatives that support advanced semiconductor manufacturing. These factors collectively encourage vertically integrated partnerships and place a premium on vendors that can offer rapid co-development cycles and localized support.Across Europe, the Middle East & Africa, the market is characterized by stringent regulatory standards, strong industrial and aerospace clusters, and a focus on telecom modernization in key markets. This region values robustness, certification readiness, and long-term availability, driving inquiries toward suppliers that provide lifecycle support and conservative technology roadmaps. Policy orientation and regional initiatives promoting secure and resilient supply chains further influence procurement preferences.

The Asia-Pacific region remains a central node for semiconductor manufacturing and assembly, with dense supplier ecosystems and fast adoption of both consumer and industrial applications. High-volume deployments, proximity to large OEMs, and investment in advanced packaging create an environment conducive to rapid innovation and scale. As a result, companies operating in this region prioritize cost-effective integration, manufacturing flexibility, and partnerships that enable quick iteration. Across all regions, decision-makers must balance sovereign policy considerations, logistical realities, and local market requirements when shaping sourcing and partnership strategies.

Key competitive differentiators and partnership models that determine vendor success in delivering integrable, protocol-flexible, and lifecycle-aware SerDes solutions

Competitive dynamics in the SerDes arena are increasingly defined by the interplay of IP depth, analog expertise, manufacturing partnerships, and systems integration capabilities. Leading suppliers differentiate through a combination of configurable IP portfolios, validated PHY stacks, and comprehensive compliance support for multi-protocol environments. In addition, firms that have invested in modular transceiver architectures and versatile analog front ends can more readily adapt to protocol shifts and emerging use cases.Partnerships between silicon providers, foundries, packaging specialists, and optical subsystem vendors have become a core determinant of competitive advantage. Companies that provide end-to-end co-design services, including signal integrity validation, thermal modeling, and cross-domain testing, are better positioned to win large-scale engagements with hyperscalers and tier-one OEMs. Moreover, vendors that offer flexible licensing models for IP cores and participate in collaborative reference designs often experience greater adoption among system integrators seeking to reduce integration risk.

Finally, firms that proactively address lifecycle support, long-term availability, and compliance documentation gain an edge in markets with stringent procurement standards such as aerospace, medical, and defense. As a consequence, both established suppliers and newer entrants must articulate clear value propositions around integration support, performance-per-watt, and roadmap stability to secure strategic partnerships and enterprise deals.

Actionable strategic measures for technology leaders to enhance resilience, accelerate integration, and drive differentiation through modular design and diversified manufacturing

Industry leaders should pursue a set of prioritized actions to capitalize on architectural shifts and to mitigate supply-side disruptions while preserving product performance and time-to-market. First, invest in modular IP and configurable PHY architectures that enable reuse across product families and support multiple interface standards; this reduces integration costs and accelerates response to protocol advancement. Second, cultivate strategic manufacturing and packaging partnerships across diverse geographies to decrease reliance on single-source supply chains and to facilitate nearshoring where policy risk is elevated.Third, embed compliance, traceability, and qualification workflows into early development phases to minimize requalification delays when assembly or foundry locations change. Fourth, align product roadmaps with emerging packaging trends such as co-packaged optics and integrated photonics by conducting joint design exercises with system integrators and optical vendors. Fifth, prioritize power-profile differentiation; create product tiers that specifically address low-power edge applications and high-performance data center deployments so that sales teams can articulate clear value propositions to each customer segment.

Finally, establish channels for ongoing engagement with key customers through regular joint validation programs and customized support agreements. By combining flexible IP strategies, diversified manufacturing footprints, and proactive compliance practices, leaders can reduce operational risk while advancing technical differentiation in a rapidly evolving SerDes landscape.

A transparent and reproducible research approach combining primary interviews, technical validation, and segmentation-driven tradeoff analysis to inform practical decision-making

This research synthesized primary interviews with domain experts, technical validation reviews, and secondary literature to construct a comprehensive view of SerDes technical and commercial dynamics. The methodology combined qualitative stakeholder interviews-spanning system architects, ASIC designers, packaging engineers, and procurement leads-with technical deep dives into reference designs and compliance test suites to ensure that insights reflect practical implementation constraints. Signal integrity analyses and architecture tradeoff evaluations were corroborated through vendor white papers and open technical standards documentation.Data collection prioritized cross-validation across multiple sources to reduce bias and to capture diverse perspectives from hyperscale operators, telecom equipment manufacturers, automotive suppliers, and defense contractors. Analytical steps included segmentation mapping across interface standards, packaging approaches, technology nodes, and power profiles to illuminate where technical requirements converge or diverge. Tradeoff matrices were developed to contrast node selection, packaging choices, and transmission media considerations in terms of integration complexity, thermal implications, and testability.

Limitations include the inherent variability of supplier roadmaps and evolving policy environments; to address this, the methodology emphasizes scenario-based analysis and sensitivity checks that focus on qualitative drivers rather than numerical forecasting. The resulting framework aims to equip decision-makers with reproducible evaluation criteria and practical validation checklists that are directly applicable to procurement and design cycles.

A concise conclusion emphasizing ecosystem integration, supply chain resilience, and holistic tradeoffs that determine sustainable differentiation in SerDes solutions

In closing, the SerDes domain is transitioning from a component-centric market to an ecosystem-driven arena where integration, packaging, and protocol flexibility determine long-term success. Organizations that adopt modular IP strategies, invest in cross-domain validation, and diversify manufacturing and packaging relationships will be better positioned to meet heterogeneous end-market requirements. At the same time, regulatory and policy developments have underscored the importance of supply chain resilience and comprehensive compliance practices as determinants of operational continuity.As technological complexity grows, collaboration between silicon designers, packaging specialists, optical vendors, and system integrators becomes indispensable. Stakeholders who institutionalize joint development programs and that place a premium on lifecycle support will reduce time-to-market risks and enhance product reliability. Ultimately, strategic choices around technology node selection, lane configurations, interface compatibility, and integration approaches should be evaluated through a holistic lens that incorporates performance, total cost, manufacturability, and regulatory exposure.

By synthesizing technical rigor with commercial pragmatism, executives and engineering leaders can convert near-term challenges into opportunities for durable differentiation and improved platform economics across a wide range of applications.

Market Segmentation & Coverage

This research report forecasts revenues and analyzes trends in each of the following sub-segmentations:- Product Type

- SerDes IP Core

- Stand-Alone SerDes

- Data Rate

- High-Speed SerDes (Greater than 50 Gbps)

- Low-Speed SerDes (Less than 1 Gbps)

- Medium-Speed SerDes (1-10 Gbps)

- Interface Type

- Ethernet

- MIPI

- PCI Express (PCIe)

- PCIe Gen 3

- PCIe Gen 4

- PCIe Gen 5

- PCIe Gen 6

- Serial RapidIO

- USB

- Channel Count

- Dual Lane

- Octal Lane

- Quad Lane

- Single Lane

- Application

- Aerospace & Defense

- Radar & Sonar Systems

- Satellite Communication Systems

- UAVs

- Automotive

- Advanced Driver Assistance Systems (ADAS)

- Autonomous Driving Systems

- In-Vehicle Infotainment (IVI)

- Consumer Electronics

- Smartphones & Tablets

- Wearable Devices

- Data Centers

- Healthcare

- Medical Imaging Systems

- Patient Monitoring Devices

- Telemedicine Infrastructure

- Industrial Automation

- Factory Automation Systems

- Industrial IoT (IIoT) Gateways

- Robotics

- Telecommunications

- 5G Wireless Infrastructure

- Optical Fiber Communication

- Aerospace & Defense

- Americas

- North America

- United States

- Canada

- Mexico

- Latin America

- Brazil

- Argentina

- Chile

- Colombia

- Peru

- North America

- Europe, Middle East & Africa

- Europe

- United Kingdom

- Germany

- France

- Russia

- Italy

- Spain

- Netherlands

- Sweden

- Poland

- Switzerland

- Middle East

- United Arab Emirates

- Saudi Arabia

- Qatar

- Turkey

- Israel

- Africa

- South Africa

- Nigeria

- Egypt

- Kenya

- Europe

- Asia-Pacific

- China

- India

- Japan

- Australia

- South Korea

- Indonesia

- Thailand

- Malaysia

- Singapore

- Taiwan

- Alphawave IP Inc

- Microchip Technology Incorporated

- Advanced Micro Devices, Inc

- Analog Devices, Inc.

- Cadence Design Systems, Inc.

- Credo, Inc.

- Faraday Technology Corporation

- HiSilicon Technologies Co., Ltd.

- Intel Corporation

- Lattice Semiconductor

- Marvell Technology, Inc.

- MediaTek Inc.

- NXP Semiconductors N.V.

- ON Semiconductor Corporation

- Renesas Electronics Corporation

- ROHM Co., Ltd.

- SK HYNIX INC.

- Sony Semiconductor Solutions Corporation

- STMicroelectronics N.V.

- Synopsys, Inc.

- Texas Instruments Incorporated

- Toshiba Corporation

- Tsinghua Unigroup Co., Ltd.

- Xilinx, Inc. by AMD

- Broadcom Inc.

Table of Contents

3. Executive Summary

4. Market Overview

7. Cumulative Impact of Artificial Intelligence 2025

Companies Mentioned

The companies profiled in this SerDes Chip market report include:- Alphawave IP Inc

- Microchip Technology Incorporated

- Advanced Micro Devices, Inc

- Analog Devices, Inc.

- Cadence Design Systems, Inc.

- Credo, Inc.

- Faraday Technology Corporation

- HiSilicon Technologies Co., Ltd.

- Intel Corporation

- Lattice Semiconductor

- Marvell Technology, Inc.

- MediaTek Inc.

- NXP Semiconductors N.V.

- ON Semiconductor Corporation

- Renesas Electronics Corporation

- ROHM Co., Ltd.

- SK HYNIX INC.

- Sony Semiconductor Solutions Corporation

- STMicroelectronics N.V.

- Synopsys, Inc.

- Texas Instruments Incorporated

- Toshiba Corporation

- Tsinghua Unigroup Co., Ltd.

- Xilinx, Inc. by AMD

- Broadcom Inc.

Table Information

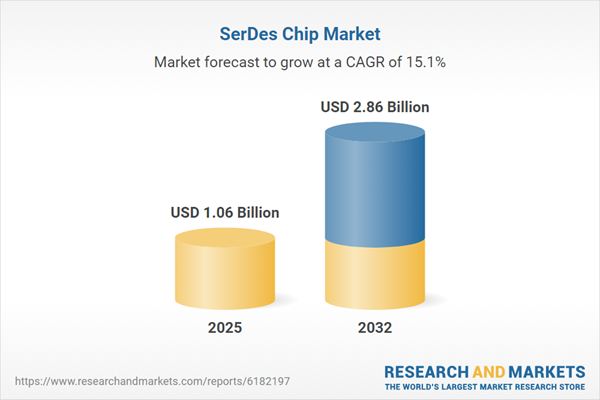

| Report Attribute | Details |

|---|---|

| No. of Pages | 193 |

| Published | November 2025 |

| Forecast Period | 2025 - 2032 |

| Estimated Market Value ( USD | $ 1.06 Billion |

| Forecasted Market Value ( USD | $ 2.86 Billion |

| Compound Annual Growth Rate | 15.0% |

| Regions Covered | Global |

| No. of Companies Mentioned | 26 |