Speak directly to the analyst to clarify any post sales queries you may have.

3D System in Package is redefining how performance, power, and footprint are optimized when silicon scaling alone no longer delivers system-level gains

3D System in Package (3D SiP) has become a practical pathway for delivering more capability in less space when traditional scaling alone cannot meet system targets. By stacking, closely integrating, and interconnecting dies and advanced components, 3D SiP enables higher bandwidth, shorter interconnect lengths, and improved functional density, which are critical for AI acceleration, high-performance computing, edge inference, advanced imaging, and next-generation connectivity. The value proposition is not simply miniaturization; it is the ability to architect systems where compute, memory, power management, and high-speed I/O are co-optimized in a constrained footprint.As design teams push performance per watt and latency budgets, packaging decisions increasingly determine end-product differentiation. This is why 3D SiP is moving from an “advanced option” to a core platform choice, especially where heterogeneous integration is required. The approach also supports faster product iteration by enabling modularity, mixing process nodes, and combining best-in-class die sources under one package-level system.

However, 3D SiP is not a single technology. It sits at the intersection of die stacking, advanced interposers, high-density substrates, through-silicon vias, micro-bump and hybrid bonding, and increasingly sophisticated thermal and reliability engineering. Consequently, executive stakeholders need a market view that connects technical feasibility to supply chain readiness, cost drivers, qualification cycles, and geopolitical risk. This executive summary frames those linkages and clarifies what is changing, what is constraining scale-up, and where competitive advantage is forming.

Heterogeneous integration, finer-pitch interconnects, and thermal-power co-design are transforming 3D SiP from a packaging choice into a system strategy

The landscape for 3D SiP is being reshaped by a decisive shift from monolithic design thinking to heterogeneous integration. Product roadmaps are now built around mixing compute chiplets, memory stacks, analog and RF components, and specialized accelerators within a single package. This shift is transformative because it changes how performance is achieved: system architects increasingly treat the package as the primary integration canvas, while the die becomes a modular building block. As a result, packaging is influencing early-stage architectural decisions rather than being a downstream execution step.In parallel, interconnect technology is undergoing a step-change. The industry is advancing from conventional bumping toward finer-pitch approaches, including hybrid bonding and advanced redistribution layers, to reduce parasitics and enable higher bandwidth. This transition is not purely about density; it is about signal integrity and power delivery at frequencies and data rates that stress traditional approaches. The practical impact is a rising need for co-design across silicon, package, and board, with verification flows that account for electromagnetic behavior, thermal gradients, and mechanical stress.

Thermal management and power integrity have emerged as the gating constraints that determine which 3D SiP configurations can scale. Higher die count and tighter integration raise localized heat flux and complicate heat extraction pathways, especially when memory stacks and compute tiles are colocated. This is pushing innovation in heat spreaders, advanced TIMs, lid designs, embedded cooling concepts, and package-level power delivery enhancements. It is also changing qualification requirements, with more emphasis on long-term reliability under cycling loads and real-world duty profiles.

Finally, manufacturing readiness is shifting the competitive center of gravity. Yield learning in multi-die assembly, known-good-die strategies, advanced metrology, and test insertion are becoming differentiators. Organizations that can tightly couple process control, defect analytics, and high-throughput inspection are better positioned to ramp complex stacks. Taken together, these shifts are making 3D SiP a strategic capability that spans design enablement, materials ecosystems, and operational excellence, rather than a narrow packaging upgrade.

U.S. tariffs in 2025 are set to reshape 3D SiP cost structures and sourcing choices by forcing process-step visibility, requalification, and design-for-resilience

United States tariff actions slated for 2025 are expected to amplify the already complex cost and sourcing calculus for 3D SiP programs. Because 3D SiP relies on a multi-step, multi-region value chain-covering wafers, substrates, interposers, bumping or bonding, assembly, test, and supporting materials-even targeted tariff measures can propagate through several tiers. The immediate effect is rarely confined to a single line item; it often appears as a combination of higher landed costs, longer procurement lead times, and increased working capital tied up in buffer inventory.A key cumulative impact is the acceleration of supply chain re-architecture. Companies with heavy exposure to cross-border flows may respond by requalifying alternate substrate suppliers, shifting assembly and test locations, or pursuing dual-sourcing for critical materials such as build-up films, copper foils, and photoresists used in advanced redistribution. For 3D SiP, requalification is not a quick administrative change; it requires engineering validation, reliability testing, and often design tweaks to accommodate process windows. Consequently, tariff-driven changes can create indirect schedule risk that must be managed like a technical risk.

Tariffs can also influence make-versus-buy decisions and partner selection. When duties increase the effective cost of outsourced steps, internalization or nearshoring may become more attractive for certain operations, particularly where IP sensitivity, rapid iteration, or yield learning is crucial. Conversely, specialized capabilities such as hybrid bonding tools, advanced lithography for redistribution, or high-end inspection may remain concentrated, making it harder to fully localize. The practical takeaway is that leadership teams should model tariff exposure at the process-step level rather than at the finished-goods level.

Over time, the most durable consequence may be strategic: tariff uncertainty encourages earlier engagement between engineering, procurement, and legal teams to align design choices with resilient supply options. Designs that tolerate broader substrate specifications, enable flexible routing of interconnect density, or support multiple assembly flows can reduce exposure. In that sense, tariffs are not only a pricing variable; they are a design constraint that is increasingly shaping the preferred architectures for 3D SiP deployments.

Segmentation insights show 3D SiP adoption depends on architecture choice, bonding maturity, end-use reliability demands, and the integration model spanning IDM to OSAT ecosystems

Segmentation reveals that adoption patterns in 3D SiP vary sharply depending on integration style, interconnect approach, and end-use performance targets. When the market is viewed through packaging architectures such as 2.5D interposer-based integration versus true 3D stacking, the trade-off between bandwidth, thermals, yield, and cost becomes clear. Interposer-centric designs often serve as a pragmatic bridge for high-bandwidth die-to-die connectivity with more manageable thermal paths, while deeper 3D stacks can unlock tighter form factors and shorter signal paths but raise compounded yield and heat extraction complexity.From the perspective of interconnect and bonding-ranging from micro-bump based stacking to emerging hybrid bonding-the segmentation highlights how performance ambitions are colliding with manufacturability realities. Finer pitch and more direct copper-to-copper connections can deliver measurable improvements in latency, energy per bit, and density, yet they demand stricter wafer and die surface preparation, tighter alignment tolerances, and more robust inline metrology. Consequently, the buying criteria for equipment, materials, and outsourced services is shifting toward process capability and yield predictability rather than nominal technical specifications alone.

Looking at segmentation by application domains such as high-performance computing, artificial intelligence accelerators, networking, consumer electronics, industrial systems, and automotive electronics, the insight is that reliability requirements and lifecycle expectations drive very different packaging decisions. Data-center-oriented designs prioritize bandwidth and power delivery with aggressive thermal solutions, whereas automotive and industrial programs emphasize qualification rigor, long-term reliability, and supply continuity. This divergence influences which 3D SiP configurations are favored, how quickly new interconnect technologies are introduced, and how conservative the ramp schedules tend to be.

Finally, segmentation by manufacturing pathway-IDM-led integration versus foundry and OSAT ecosystems-shows that collaboration models are becoming a competitive lever. IDM-led programs may move faster when design, process, and test are tightly coordinated, while ecosystem-driven programs benefit from broader supplier optionality and access to specialized steps. Across all segments, the strongest outcomes occur when silicon design, package design, and test strategy are planned together, reducing late-cycle surprises around warpage, thermal throttling, and known-good-die assumptions.

Regional insights highlight how manufacturing depth, end-market demand, and resilience priorities in the Americas, Europe, Middle East & Africa, and Asia-Pacific shape 3D SiP strategies

Regional dynamics in 3D SiP are defined by how each geography combines advanced manufacturing capability, supply chain depth, and end-market pull. In the Americas, demand is strongly influenced by data center build-outs, AI infrastructure, aerospace and defense electronics, and high-value product design activity. This region’s strategic focus increasingly centers on supply resilience, domestic capability expansion, and partnerships that ensure access to advanced substrates, assembly capacity, and packaging talent, especially as policy and trade considerations reshape sourcing decisions.In Europe, the 3D SiP narrative is closely tied to industrial automation, automotive electrification, and edge computing deployments that require high reliability and long program lifetimes. The region’s strength in automotive and industrial systems pushes packaging decisions toward robust qualification and traceability practices, which in turn influences material choices, test coverage, and vendor selection. Europe’s approach often emphasizes ecosystem coordination, aligning research institutions, equipment suppliers, and manufacturers to secure capability across the value chain.

The Middle East and Africa region is emerging primarily through downstream adoption, infrastructure investment, and growing interest in technology sovereignty initiatives. While large-scale 3D SiP manufacturing concentration is limited compared to other regions, the opportunity lies in demand for advanced compute infrastructure, secure systems, and new industrial projects that can pull in high-performance modules. This can create targeted opportunities for partnerships, packaging services, and regional assembly or test initiatives where economics and policy align.

Asia-Pacific remains the most concentrated hub for advanced packaging scale, supported by deep supplier networks across substrates, materials, equipment, assembly, and test. Strong consumer electronics production, dense semiconductor manufacturing clusters, and rapid iteration cycles make the region pivotal for bringing new 3D SiP configurations into volume. At the same time, concentration risk and cross-border dependencies are increasingly visible, leading global stakeholders to balance Asia-Pacific’s scale advantages with multi-region redundancy and qualification strategies. Across regions, the competitive differentiator is not merely presence but the ability to coordinate design enablement, manufacturing execution, and logistics resilience as one operating system.

Company insights reveal competition across foundries, OSATs, materials, and equipment players where ecosystem coordination and yield-reliability execution define leaders

Company activity in 3D SiP reflects a multi-layered competitive environment where leadership is defined by ecosystem orchestration as much as by any single proprietary technology. Foundries are expanding advanced packaging portfolios to keep heterogeneous integration close to wafer fabrication, enabling tighter co-optimization and faster yield learning. OSATs are investing in higher-density redistribution, advanced substrate handling, and next-generation bonding to remain central to multi-die assembly at scale. IDMs and fabless leaders are simultaneously pushing custom integration approaches to differentiate performance, power, and form factor in their flagship platforms.Materials and substrate suppliers play an outsized role because substrate availability and quality often constrain ramp schedules. Innovations in build-up films, low-loss dielectrics, and copper processes can directly influence signal integrity, warpage control, and reliability. Likewise, equipment vendors that provide high-precision placement, bonding, metrology, and inspection are becoming strategic partners, as their process windows and throughput determine how quickly complex stacks can be industrialized.

A notable competitive pattern is the rise of co-development agreements spanning silicon design, packaging, and test. Companies that can offer reference flows, proven design rules, and integrated test strategies reduce adoption friction for customers moving into 3D SiP. In contrast, fragmented engagement models can lead to late-cycle redesigns driven by thermal constraints, yield excursions, or unexpected reliability failures.

Across the competitive set, differentiation is increasingly visible in three areas: the maturity of design enablement (PDKs, chiplet interfaces, and co-design tools), the ability to deliver consistent yield in multi-die assembly, and the discipline of end-to-end reliability qualification. As customers demand shorter time-to-market and higher confidence in long-life performance, companies that industrialize these capabilities will capture the most durable relationships and platform wins.

Actionable recommendations focus on co-design governance, supply-flexible qualification, test-first architecture, and yield learning systems that scale 3D SiP programs

Industry leaders can strengthen 3D SiP outcomes by treating packaging as an architectural decision that begins at concept definition. That means establishing cross-functional governance where silicon architects, package engineers, thermal specialists, and supply chain owners jointly decide which functions are integrated, which interfaces are standardized, and which risks are accepted. When this operating model is in place, teams can avoid late changes that typically arise from overlooked thermal bottlenecks, power integrity gaps, or substrate feasibility constraints.A second recommendation is to design for supply flexibility without compromising performance targets. Leaders can pursue dual-qualified materials where feasible, align substrate stack-ups to multiple supplier capabilities, and build assembly flows that can be transferred across sites with minimal redesign. Given the likelihood of tariff-driven and geopolitical disruptions, investing early in qualification plans and configuration alternatives can reduce schedule volatility and protect product launches.

Third, organizations should elevate test strategy to a first-class design input. Known-good-die assumptions, test access points, and repair or redundancy concepts can materially influence effective yield in multi-die stacks. By aligning wafer sort, intermediate test, and final test with the package architecture, teams can lower hidden costs and reduce the risk of field failures. This is especially critical in high-reliability segments where returns and reputation damage are disproportionately expensive.

Finally, leaders should build a learning loop that connects inline metrology, defect analytics, and reliability outcomes to design rules and supplier scorecards. The most successful programs institutionalize yield learning across product generations rather than relearning the same failure modes each cycle. Over time, this creates a compounding advantage: faster ramps, fewer escapes, and clearer decision-making on when to adopt next-generation bonding or higher-density routing. The organizations that win will be those that operationalize 3D SiP as a platform capability, not a one-off engineering project.

Methodology combines value-chain mapping, technical literature synthesis, and primary ecosystem validation to ground 3D SiP insights in execution realities

The research methodology integrates structured secondary research with rigorous primary validation to reflect current technology directions and operational realities in 3D SiP. The process begins by mapping the value chain across wafers, interconnect formation, substrates and interposers, assembly and bonding, inspection and metrology, test, and end-use integration. This framing ensures that insights capture both technical drivers and supply-side constraints that shape adoption decisions.Secondary research synthesizes publicly available technical literature, standards activity, corporate disclosures, patent themes, conference proceedings, and regulatory developments relevant to advanced packaging and cross-border trade. This step is used to define terminology consistently, identify key technology milestones, and establish an evidence-based view of where manufacturing capability is scaling and where constraints persist.

Primary research then validates and refines these findings through interviews and structured discussions with stakeholders across the ecosystem, including engineering leaders, operations and quality managers, sourcing professionals, and executives involved in packaging strategy. These conversations focus on practical issues such as yield learning, thermal constraints, equipment readiness, qualification timelines, and supplier selection criteria. Inputs are cross-checked for consistency, with attention paid to separating directional consensus from isolated opinions.

Finally, the analysis applies triangulation across sources and stakeholder perspectives to produce a cohesive narrative of market structure and decision drivers without relying on a single viewpoint. Quality control includes logic checks for internal consistency, careful handling of policy-related statements such as tariffs, and clear differentiation between observed practices and forward-looking strategic implications. The result is a methodology designed to support decision-grade understanding of 3D SiP adoption, risks, and execution priorities.

Conclusion underscores 3D SiP as an integration discipline shaped by thermal-test realities and 2025 policy pressures, rewarding resilient platform execution

3D System in Package has moved into a phase where success is defined by integration discipline and ecosystem readiness, not by isolated breakthroughs. The most important changes are occurring at the interfaces: between chiplets and memory stacks, between package routing and board constraints, and between thermal limits and real application workloads. Organizations that treat these interfaces as design-first priorities are better positioned to deliver differentiated systems with predictable ramps.At the same time, external pressures are intensifying. Tariff developments in 2025 and broader geopolitical uncertainty are pushing companies to reconsider sourcing, qualification, and manufacturing footprints. These forces reinforce a central message: resilience must be engineered into the product and the supply chain simultaneously, because late-stage mitigation is costly and slow in advanced packaging.

Across applications and regions, the trajectory is clear. 3D SiP will continue to expand where it enables higher bandwidth, lower latency, and tighter form factors, but it will do so with heightened scrutiny on thermals, reliability, and test. The winners will be those who combine technical ambition with operational realism, establishing repeatable integration platforms that can absorb new bonding methods and material innovations without destabilizing product delivery.

Table of Contents

7. Cumulative Impact of Artificial Intelligence 2025

16. China 3D System in Package Market

Companies Mentioned

The key companies profiled in this 3D System in Package market report include:- Amkor Technology Inc

- ASE Group

- ChipMOS TECHNOLOGIES INC

- Fujitsu Limited

- HP Inc

- Huatian Technology

- IBM Corporation

- Intel Corporation

- Interconnect Solutions Inc

- Jiangsu Changjiang Electronics Technology Co Ltd

- Kyocera Corporation

- Micron Technology Inc

- NEO Semiconductor Inc

- NVIDIA Corporation

- Powertech Technology Inc

- Qualcomm Technologies Inc

- Renesas Electronics Corporation

- Samsung Electronics Co Ltd

- Siliconware Precision Industries Co Ltd

- Sony Corporation

- STATS ChipPAC

- STMicroelectronics

- Taiwan Semiconductor Manufacturing Company

- Texas Instruments Incorporated

- Toshiba Corporation

- Unimicron Technology Corporation

- Vanguard International Semiconductor Corporation

Table Information

| Report Attribute | Details |

|---|---|

| No. of Pages | 185 |

| Published | January 2026 |

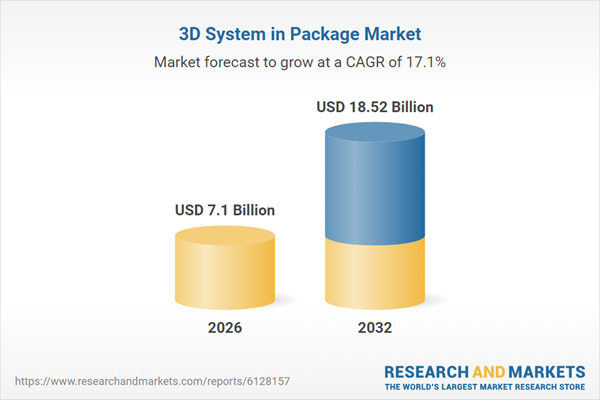

| Forecast Period | 2026 - 2032 |

| Estimated Market Value ( USD | $ 7.1 Billion |

| Forecasted Market Value ( USD | $ 18.52 Billion |

| Compound Annual Growth Rate | 17.1% |

| Regions Covered | Global |

| No. of Companies Mentioned | 28 |